Imec研究协会的半导体市场展望

英特尔、三星以及台积电等厂商都有可能发布自己的下一代晶体管产品。之所以各寻出路,是因为在面对几乎无法突破的技术极限之后,半导体发展路线图开始呈现发散的整体态势。

在一年一度的大会活动当中,Imec研究人员们列出了一份被行业观察者们称为“寒武纪爆发”的选项清单,旨在为这条似乎已经走不通的道路找到新的突破口。这份清单当中包含多种晶体管设计、材料、架构以及封装方法。

Imec研究协会首席执行官Luc van den Hove在主题演讲当中表示,“通用型设备也许不再有发展空间……一线形式的路线图也可能无法满足需求。未来还不明确,但我们显然需要更多选项。”

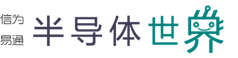

鉴于Imec所展示的发展路线图已经非常清醒地体现出我们对于当前困境的理解,工程师们将能够从中获得后续探索所需要的一切手段。从尺寸上看,这份路线图预计下几代芯片都将只能在个位数纳米级别区间内行进。换言之,栅极长度超过40纳米,金属间距为16纳米以及节点尺寸2纳米恐怕已经是物理层面的真正极限。

研究人员们展示了一份坦率而积极的发展路线图,其中N7与目前晶圆代工厂生产的N5节点类似。

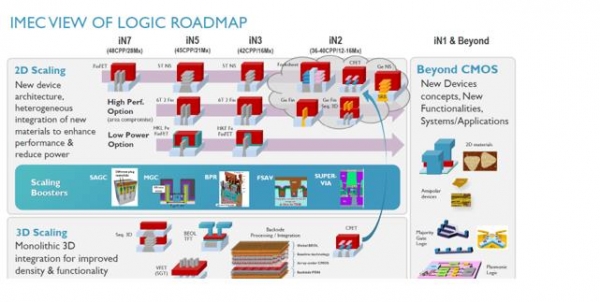

结果就是,芯片的性能可能将无法满足高端使用场景的需求。虽然有效功率已经封顶,但在某些情况下现有芯片方案仍存在改进空间,特别是那些愿意从FinFET转向更为紧凑的纳米片晶体管的设计方案。

在另一方面,专注于为各类移动系统缩小芯片尺寸并实现功率控制的芯片制造商可能还将继续长期依赖于FinFET。相反,那些狂热希望获得进一步性能提升的人们则会提前转向纳米片设计,Imec公司预计这将使芯片的主频增加8%,但代价就是芯片尺寸无法缩小。

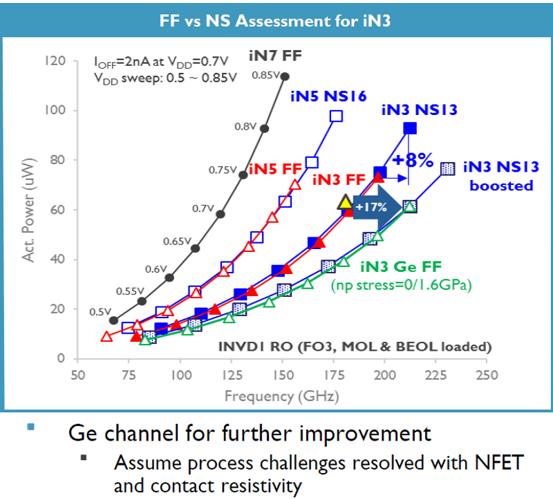

纳米片实际上代表着被Imec此前称为forksheet的一种新兴技术的中间产物。这种设计的实质,在于缩短n与p元件之间的距离。紧凑型晶体管的终极形态就是互补或者垂直FET,其通过堆叠n与p元件将FET落实在四个甚至三个轨道之上。

在此过程当中,工程师们可能会尝试将基板的k值降低至3.3,甚至最终突破原本的天竺葵结构。Imec逻辑扩展计划主管Julien Ryckaert表示,“其中很多设计都是我们独创的。”

在标准单元与更高级别上工作的设计人员则不需要太多关注晶体管本身的变化;但如果他们希望改变晶圆代工厂的生产方式,则需要接受额外的交叉检查。Imec项目主管Diederik Verkest表示,毕竟拥有自己内存宏与单元库的晶圆代工企业也需要“深入理解技术方面正在发生的变化。”

纳米片(简称NS)预计将在未来全面超越FinFET(简称FF)。

少数新兴的晶圆、芯片与晶体管堆栈将提供额外的性能提升空间,进而从根本上挑战传统的SoC。然而,这些技术在设备校准与冷却方面也面临着自己的独特挑战——具体来讲,此类设计也许会将发热量提升至500瓦级别。

Imec方面还描述了SoC的全面改造方向,也就是有序3D——其将对电源、逻辑以及存储器电路的不同需求进行拆分与优化。其中一个版本将功率传输电路放在晶圆背面,减薄至几百纳米,并利用微小的硅通孔进行连接。

另一个更具野心的版本则利用铜接铜键将SRAM缓存安放在核心上方的载体晶圆上。最终的有序3D结构将呈现出三明治式设计,底部为SRAM阵列,顶部为电源电路,中间则是核心逻辑。其目标在于最大限度提升SRAM尺寸,同时降低制造成本。

随着晶体管通过互补式FET被缩小为3到4轨道设备,内埋供电轨道(简称BPR)将成为一种普遍性设计

这套方案为各类设备(例如无供电器件)的集成开启新的大门。然而,Imec在最初的5纳米演示方案中并未提供任何有源结构。

Ryckaert表示,“这将是一片新的天地……这里已经存在一份完整的发展路线图,所以摩尔定律还没有过时。”

如果要进一步冲击1到2纳米节点,工程师们则需要放弃铜与钴材料,转而使用钌等新的金属载体。这类材料使得设计师能够确保其不致扩散到二氧化硅屏蔽层当中。

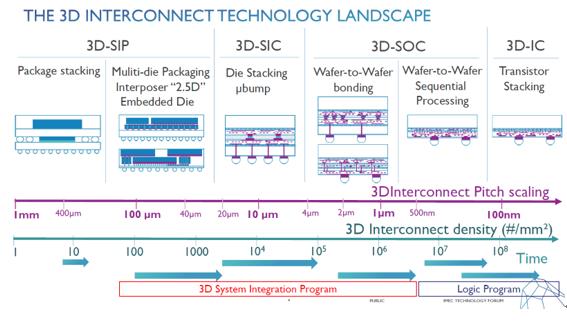

除了晶片层面之外,研究人员还讨论了另外六种新的封装技术。举例来说,Imec方面正在开发一种成本更为低廉的英特尔EMIB变体,其将桥接基板集成至一套封装当中。其它选项还包括将互连机制的尺寸缩小至数百微米甚至数十纳米甚至级别。

Imec 3D芯片项目管理研究员Eric Beyne指出,“在某些情况下,我们需要关注的已经不再是单一逻辑节点……但可以肯定的是,没有哪种封装技术能够满足一切需求。”

密度极高的堆栈将使得设备的耗散水平达到数百瓦,因此Beyne的团队正致力于开发3D打印塑料帽,用于为设备提供水冷辅助。

晶圆、晶片与晶体管封装选项涵盖从几微米到数纳米的广阔区间

然而,封装发展路线图仍然受到设备能力方面的限制。同样的,用于设计电路系统的EDA工具也还没有准备就绪。但他表示,“我们已经发现了一条有望走通的道路。”

英特尔公司首席技术官Mike Mayberry在主题演讲中表示,这些变化代表着传统半导体技术的最新发展方向。

传统处理器将与新的、特定于某些领域的加速器共存,微软在自家数据中心之内利用x86处理器与FPGA相结合的作法就是很好的例子。他最后总结称,“当我们不确定前路在何方时,这些案例带来了很好的启发……摩尔定律仍在继续,只是发展出了混合匹配的功能与架构,旨在应对日益提高的数据产生速度。”