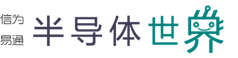

随着半导体技术的持续演进,传统的二维芯片缩放规则受到物理极限的挑战,尤其是摩尔定律在微小化方面的推进速度放缓。为了继续保持计算性能和存储密度的增长趋势,业界开始转向三维集成电路设计与封装技术的研发。混合键合技术就是在这样的背景下应运而生,作为一种创新的互连解决方案,它能够将不同功能的芯片或晶圆以垂直堆叠的方式进行集成,从而实现更高的集成度、更快的数据传输速度以及更低的功耗。

混合键合(Hybrid Bonding)是一种先进的集成电路封装技术,主要用于实现不同芯片之间的高密度、高性能互联。这种技术的关键特征是通过直接铜对铜的连接方式取代传统的凸点或焊球(bump)互连,从而能够在极小的空间内实现超精细间距的堆叠和封装,达到三维集成的目的。

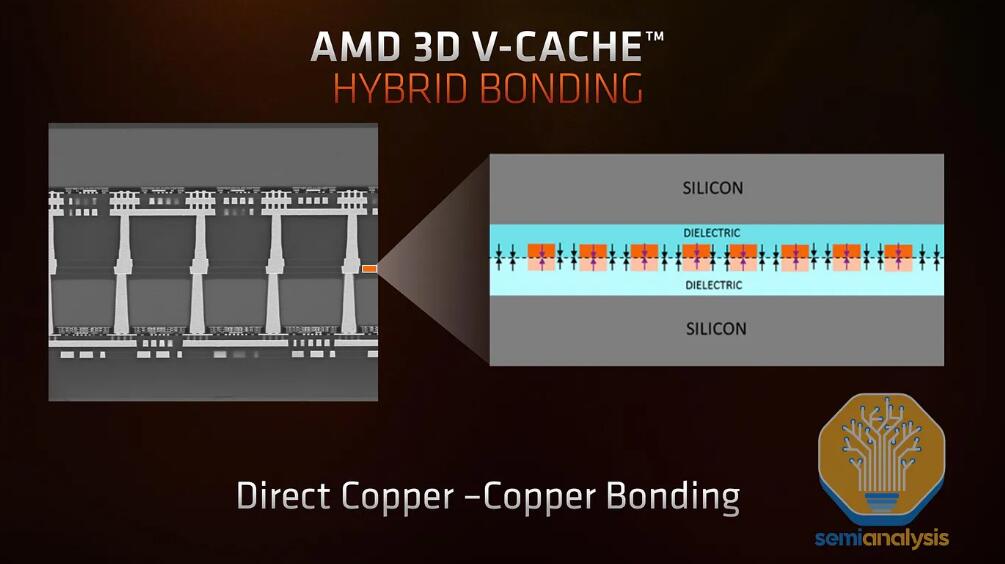

在混合键合工艺中,两个或多个芯片的金属层(通常是铜层)被精密对准并直接压合在一起,形成直接电学接触。为了保证良好的连接效果,需要在芯片表面进行特殊的处理,例如沉积一层薄且均匀的介电材料(如SiO2或SiCN),并在其上制备出微米甚至纳米级别的铜垫和通孔(TSV)。这些铜垫和通孔将芯片内部的电路与外部相连,使得数据传输速度更快、功耗更低,同时极大地提升了芯片的集成度。

混合键合技术的优势包括:

极高密度互连:相较于传统键合技术,混合键合可以实现亚微米级乃至纳米级的互连间距,允许在更小的面积上放置更多的连接点,大大增加了芯片间的数据通信带宽。

低电阻、低延迟:由于省去了中间介质如焊锡等材料,直接铜对铜的连接具有更低的电阻,降低了信号传输的能量损失,同时也减少了信号传播的时间延迟。

更好的散热性能:紧凑的结构和直接的导电路径有助于改善热管理,降低发热问题,对于高性能计算、人工智能和其他高速运算应用尤其重要。

小型化与高性能封装:混合键合技术推动了2.5D和3D封装的发展,使得芯片能够以垂直堆叠的方式整合到一起,显著缩小了最终产品的体积,并提升整体系统性能。

目前,混合键合技术已被各大半导体厂商如英特尔、AMD、台积电、三星等采用,在图像传感器、高端处理器、HBM内存堆栈、AI加速器等领域取得了突破性进展。然而,混合键合技术的实施也面临着诸多挑战,如严格的洁净室环境要求、高精度对准工艺、以及确保大面积晶圆上数十亿个连接点都成功键合的良率控制等难题。尽管如此,随着市场需求和技术进步,混合键合将继续成为未来先进封装领域中的关键技术之一。

目前常见的应用场景:

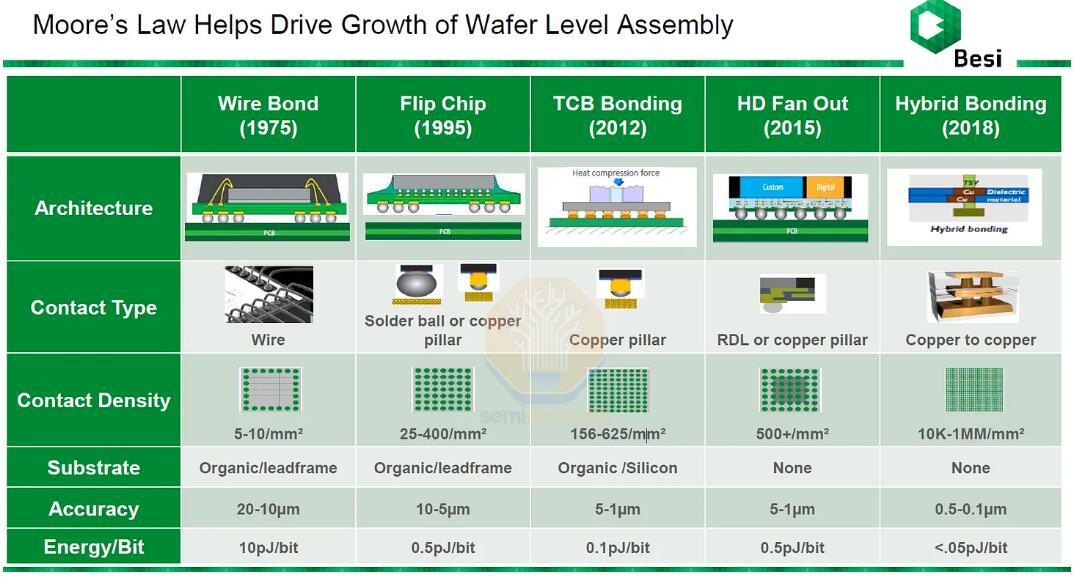

1. 3D芯片堆叠:混合键合被广泛应用于处理器和内存堆栈中,例如AMD的3D V-Cache技术和HBM高带宽内存的多层堆叠。通过混合键合,可以将CPU与额外缓存芯片紧密连接在一起,显著提升系统性能;同时,在图形处理单元(GPU)和高性能计算领域,将内存芯片直接堆叠到逻辑芯片上,极大地提高了数据带宽和访问效率。

2. 异构集成:混合键合技术也促进了异构系统的集成,使得各种不同工艺节点制造的芯片可以有效地结合在一起,形成一个单一的高性能封装体。例如,将射频芯片、传感器、处理器等多种类型的芯片整合在同一封装内,优化了物联网设备、智能手机和其他智能硬件的空间利用和整体性能。

3. 图像传感器:混合键合在CMOS图像传感器领域也有重要应用,如背照式(BSI)传感器和堆叠式传感器等,其中底层的像素阵列通过混合键合技术与顶层的电路层相连,降低了光路损失并实现了更小型化的相机模组设计。

4. 汽车电子与5G通信:对于需要高度集成、低延迟和高效能的汽车雷达、自动驾驶芯片以及5G基站和终端芯片而言,混合键合技术提供了一种理想的封装方案,有助于提高系统可靠性,并满足严苛的应用环境需求。

混合键合作为先进封装技术的核心组成部分,正逐渐成为推动半导体行业向三维集成发展的重要驱动力,并在众多关键市场领域发挥着越来越重要的作用。随着技术不断成熟和成本效益的提高,预计未来混合键合技术将在更多复杂且要求极高的系统级封装解决方案中得到广泛应用。