不久前,有消息称,台积电在2纳米先进制程研发上取得重大突破,已成功找到路径,将切入环绕式栅极技术(gate-all-around,简称GAA)技术。

利用成熟的特色工艺追求更先进的制程,一直是台积电和三星等芯片厂商致力的方向。此前,三星声称将在3纳米率先导入GAA技术,表达了其取得全球芯片代工龙头地位的野心。此次台积电在2纳米制程研发上取得重大突破,凸显了其强大的研发实力,也让两大芯片代工巨头的竞争加剧。

台积电、三星角逐更先进制程

摩尔定律诞生之后,芯片的尺寸越来越小,企业不断摸索新的工艺和材料发展半导体产品、改进性能。半导体行业专家莫大康告诉《中国电子报》记者,目前半导体行业的主要发展路线是尺寸的不断缩小。尺寸的缩小能够带来集成度的提升,增强产品的性能,也能够降低产品的成本。

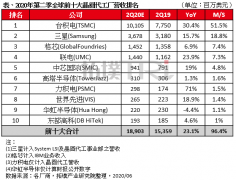

台积电和三星是芯片代工领域的佼佼者。据集邦咨询数据,今年第二季度,台积电拿下了51.5%的芯片代工份额,高居榜首,三星则以约19%的份额紧随其后。中国电子专用设备协会秘书长金存忠指出,台积电在7纳米量产的时程上领先于三星。对此,复旦大学微电子学院副院长周鹏给出了更具体的信息:台积电早于2018年4月宣布实现7纳米制程量产,获得了苹果、华为海思、AMD、高通等客户的大量7纳米订单。而三星在2018年10月宣布其7纳米工艺实现量产,时程的落后导致大量客户订单流失。

在先进制程领域,台积电和三星不断展开“角逐”。以5纳米制程为例,台积电拿下了今年下半年苹果即将推出的四款iPhone新机处理器的全部订单。金存忠告诉记者,预计台积电今年5纳米可实现量产,但三星却无法做到这点。看到台积电拿下大量5纳米订单的三星果然不甘落后,宣布将此前的7纳米制程芯片基地改造为5纳米制程生产基地,为第三方厂家提供芯片代工服务,试图用“急冲”5纳米的方式追赶台积电。据悉,目前三星已获得部分高通5G芯片代工订单,将采用5纳米制程生产芯片。

在更先进制程的竞争中,台积电和三星依旧“你追我赶”。周鹏介绍,三星在更先进制程的研发上投入了大量资金,同时也对芯片工艺路线图作出了调整,将跳过4纳米工艺,由5纳米直接上升至3纳米,并在3纳米工艺中率先宣布将使用GAA技术。三星还基于纳米片制造出了MBCFET(多桥式-沟道场效应晶体管),可显著增强晶体管性能,以取代FinFET晶体管技术。

莫大康告诉记者,尽管台积电在GAA架构的开发时程上落后于三星,但台积电计划在3纳米制程中仍采用FinFET技术,减少生产工具的变更能保持其成本结构的稳定,同时也能减少客户的设计变更,降低其生产成本,或会产生更好的效果。周鹏声称,台积电多年前已开始谋划3纳米工艺,计划于2021年实现量产。在下一个节点2纳米上,台积电似乎领先一步,此次他们在2纳米先进制程研发上取得的重大突破已说明了这点。据悉,台积电宣布在中国台湾的南方科技园建厂,启动2纳米工艺的研发工作,预计最快在2024年投产。而三星在2纳米制程的研发上鲜有消息对外披露。

台积电因何能在更先进制程“一马当先”?

在摩尔定律的“指挥棒”下,晶圆代工更先进制程的竞争激烈程度愈演愈烈。周鹏告诉记者,在先进制程方面,三大芯片代工巨头台积电、三星和英特尔处于第一阵营。英特尔有计划在2021年推出7纳米(相当于5纳米),但目前仍主要坚守在10纳米节点,希望将10纳米做到“极致”,因此7纳米及以下工艺节点的战场就只剩下台积电和三星,呈现绝对的寡头竞争格局。这回台积电在2纳米先进制程研发上有了重大突破,意味着台积电在更先进制程方面暂时处于领先地位。那么,台积电因何能在更先进制程上“一马当先”呢?

莫大康介绍,其实台积电并不是“一个人在战斗”,台积电能够“超前”在2纳米技术上获得突破,得益于其背后有着庞大的群体在支持。据悉,台积电始终强调,在做代工的同时时刻保持中立态度,不会与客户争抢订单,同时也能够真正做到把客户的利益放在第一位。因此台积电长期以来能够与客户建立良好的关系,使得与台积电无利益冲突的客户群(苹果、赛灵思、英伟达等)数量非常庞大。芯片在进入3纳米制程后,现有的很多技术难以满足需求,作为代工厂的台积电也不例外,需要从器件的架构、工艺变异、热效应、设备与材料等方面综合解决。然而,由于台积电背后拥有庞大的客户群体在支持着它,能够与台积电共同改善制程良率、降低成本,来加快量产速度,而这也是台积电能够在2纳米领域“先发制人”的关键。

周鹏指出,台积电在FinFET技术上的优势为台积电在2纳米先进制程的研发提供极大助力,使其占得先机。“随着工艺节点发展到3nm后,晶体管沟道进一步缩短,FinFET结构遭遇量子隧穿效应的限制。GAA-FET则相当于FinFET的改良版,FinFET的栅极包裹沟道3侧,与FinFET控制栅极漏电流的机理类似,GAA技术则将沟道四侧全部包裹,进一步提升栅极对沟道电流的控制能力。台积电在FinFET技术领域具备深厚底蕴,这些科技积累为台积电成功由3纳米FinFET技术切换至2纳米GAA技术起到了重要推动作用,大大缩短了台积电先进制程技术更新迭代周期。”周鹏对记者说。

同时,台积电在设备支持上也做好了准备。周鹏声称,为实现2纳米先进制程,台积电已经大批量订购了ASML极紫外光刻机(EUV)设备。然而,周鹏也指出,光刻技术的精度直接决定制程的精度,对于2纳米的先进制程,高数值孔径的EUV技术还亟待开发,光源、掩模工具的优化以及EUV的良率和精度都是实现更先进制程技术突破的重要因素。

台积电突破或刺激其他厂商技术升级

更先进制程的重大技术突破会影响整个集成电路产业和市场格局。周鹏声称,虽然对制程技术的评估需要从实际晶体管的密度、性能以及功耗等多个维度进行考量,但先进制程重大技术的推出对于集成电路产业和市场格局有重大意义。“在先进制程的研发过程中,每条技术产线成本投资都超过百亿美元。更高的研发和生产成本,对应的是更难的技术挑战。每当制程工艺逼近物理极限,晶体管结构、光刻、沉积、刻蚀、集成、封装等技术的创新与协同配合,能对芯片性能天花板的突破起到决定性作用。”周鹏对记者说。

周鹏还告诉记者,先进工艺节点的研究对于代工厂商以及整个半导体行业的发展都至关重要,研发的迟滞必将被其他厂商的先进制程所超越甚至替代。基于此,周鹏认为,此次台积电在2纳米制程的技术突破对三星、英特尔等龙头企业在先进制程领域的产品开发与技术升级能起到一定刺激作用。

周鹏预测,由于台积电3纳米工艺预定在2021年量产,其2纳米的推出可能位于2023到2024年之间。那么,如果台积电顺利推出2纳米制程,这是否会使未来代工市场的格局发生变化?周鹏声称,2纳米制程的率先推出,定然会进一步扩大台积电在先进制程市场份额的占比,甚至可能会拉开与三星和英特尔的差距。当然,三星和英特尔也在积极推进研发。工艺技术的研发充满变数,未来谁能最终领先还需进一步观察。

对于代工市场上先进制程的竞争,周鹏声称,这种竞争可以为整个集成电路行业和用户带来益处。“市场的需求驱动着先进制程的进一步开发,无论未来先进制程的引领者是谁,最终受益的将是整个集成电路行业以及享用高性能电子产品的每一个人。”周鹏对记者说。